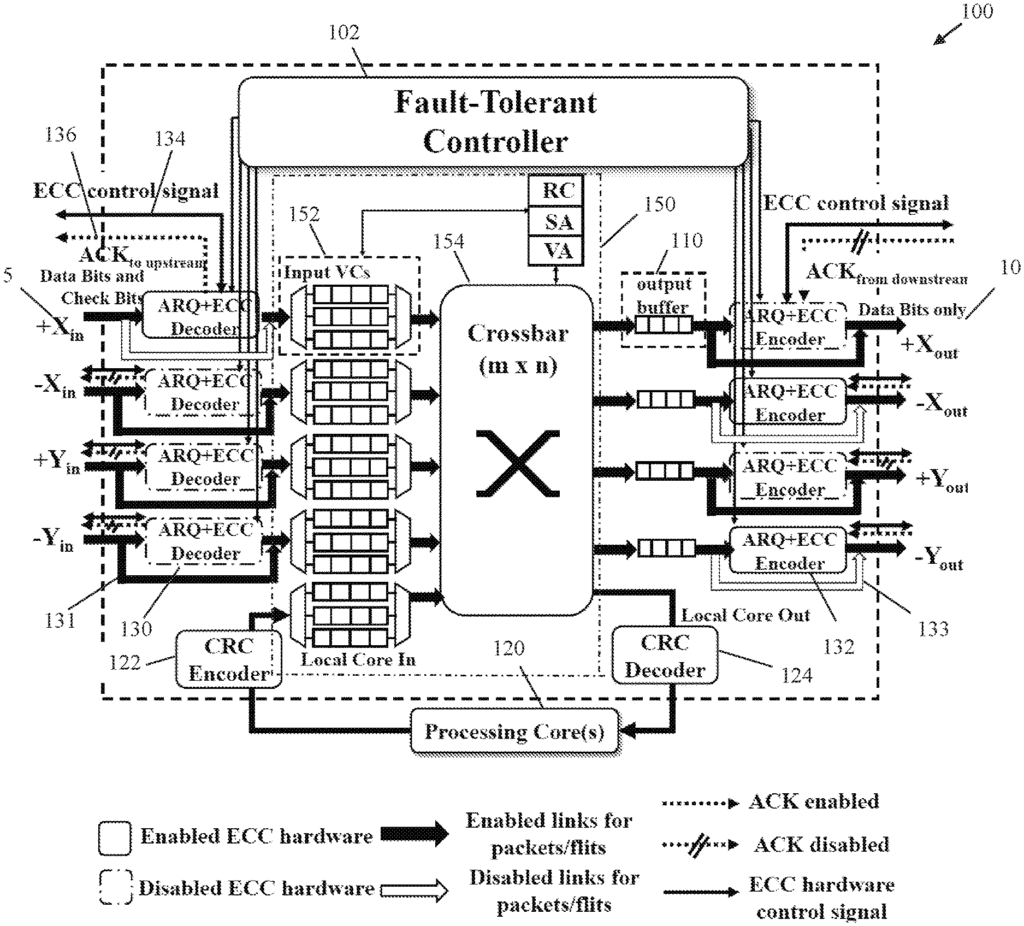

In the fast-paced world of semiconductor technology, designing chips that are both high-performance and energy-efficient is more critical than ever. With increasing demand for powerful computing across industries, the challenge lies in balancing performance with energy consumption and fault tolerance. Our breakthrough framework for on-chip communication offers an innovative, learning-based solution that addresses these demands head-on.

The Challenge

Traditional on-chip communication frameworks often struggle to keep up with the ever-increasing data flow in modern chips. This bottleneck limits performance and increases energy consumption, particularly in high-demand environments such as AI, data centers, and edge computing. Moreover, ensuring fault tolerance without sacrificing performance or efficiency presents a major hurdle in semiconductor design.

The Solution

Our learning-based communication framework solves these challenges by optimizing on-chip communication in real time, ensuring the highest levels of performance while minimizing energy usage. This intelligent system continuously adapts to data flow, allowing chips to operate more efficiently under varying workloads. Additionally, its fault-tolerant design ensures that even in the presence of failures, chips continue to function with minimal disruption.

Why This Matters

- Energy Efficiency and Performance: With energy efficiency becoming a priority across industries, this framework reduces power consumption while boosting chip performance. Whether applied in data centers, AI applications, or consumer electronics, this technology helps reduce costs and environmental impact.

- Fault Tolerance: This framework doesn’t just offer high performance—it’s built to withstand failures. In industries where downtime is costly or dangerous, such as automotive and telecommunications, this technology ensures that systems remain operational even when faults occur.

- Learning-Based Optimization: By using AI to optimize on-chip communication, this framework continuously improves chip performance, making it a future-proof solution that adapts to evolving demands.

Why License This Technology?

Licensing this innovative communication framework gives your company the tools to design chips that are smarter, faster, and more efficient. In an industry where the demand for energy-efficient, high-performance semiconductors is growing exponentially, this solution offers a competitive edge. It enables your products to stand out by delivering not just raw power, but intelligent performance management that maximizes efficiency and reliability.

The Opportunity

As industries increasingly rely on advanced semiconductor technology, now is the time to adopt frameworks that will define the next generation of chips. License this learning-based, fault-tolerant communication design and take a bold step into the future of semiconductor innovation.