Efficient Electronics with Direct Graphene Synthesis

Introduction

Graphene is one of the most promising materials in modern science, known for its exceptional electrical, thermal, and mechanical properties. However, one of the biggest challenges in leveraging graphene’s potential lies in the complexity of synthesizing high-quality graphene films on various substrates. Our patented method for the direct synthesis of reduced graphene oxide (rGO) films on dielectric substrates offers a highly efficient and scalable solution. This technology brings graphene closer to large-scale applications in electronics, nanotechnology, and semiconductor industries, offering a new path for developing high-performance devices.

Barriers in Traditional Graphene Synthesis

While graphene’s potential in electronics and nanotechnology is immense, traditional methods of producing graphene or reduced graphene oxide films are often cumbersome and inefficient. These processes frequently involve multiple steps, requiring transfer from one substrate to another, which increases the risk of defects, contamination, and performance degradation. The inability to directly synthesize graphene films on key substrates such as dielectrics limits the material’s application in next-generation devices, including transistors, sensors, and flexible electronics.

In industries where precision, scalability, and material performance are critical, there is a growing need for simpler, more reliable methods to integrate graphene films directly onto dielectric substrates without compromising quality or functionality.

Direct Synthesis for Seamless Integration

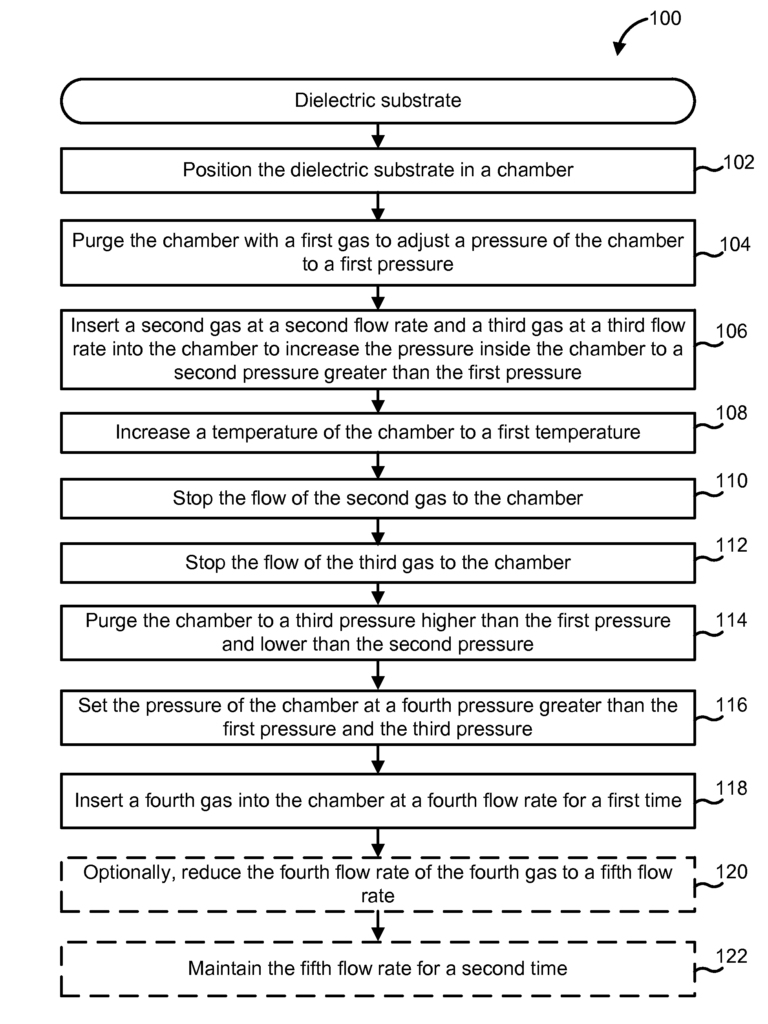

Our patented method provides a direct synthesis approach, allowing for the formation of reduced graphene oxide films directly on dielectric substrates. This method streamlines the process by eliminating the need for transfer steps, reducing potential defects, and maintaining the structural integrity of the graphene oxide during reduction. The resulting films are of high quality, with enhanced electrical conductivity and thermal properties, making them ideal for applications in electronic devices, flexible electronics, and nanoelectronics.

This direct synthesis approach is not only more efficient but also scalable, enabling the production of high-performance graphene-based materials for a wide range of industrial applications. Whether in developing high-speed transistors, sensors, or advanced circuit components, this technology offers a more seamless integration of graphene into existing manufacturing processes, unlocking new possibilities in the electronics and nanotechnology sectors.

Key Benefits

- Direct Integration: Synthesize reduced graphene oxide films directly on dielectric substrates, eliminating transfer steps and reducing defects.

- Improved Material Performance: Enhanced electrical and thermal properties of the rGO films make them suitable for high-performance electronic applications.

- Scalable Process: Ideal for large-scale production in industries such as semiconductors, electronics, and nanotechnology.

- Versatile Applications: Suitable for use in transistors, sensors, nanoelectronics, and flexible electronic devices.

Enhance Electronic Devices with Directly Synthesized Graphene Films

Licensing this direct synthesis technology provides companies in electronics, nanotechnology, and materials science with an advanced solution for integrating graphene into next-generation devices. With its ability to streamline the production process while delivering high-quality films, this technology offers a powerful tool for developing more efficient, scalable, and high-performance electronic components.

- Abstract

- Claims

What is claimed is:

Share

Title

Direct synthesis of reduced graphene oxide films on dielectric substrates

Inventor(s)

Anirudha V. Sumant, Richard Gulotty

Assignee(s)

UChicago Argonne LLC

Patent #

10351429

Patent Date

July 16, 2019