Efficient Circuit Design with Data Regression Models

Introduction

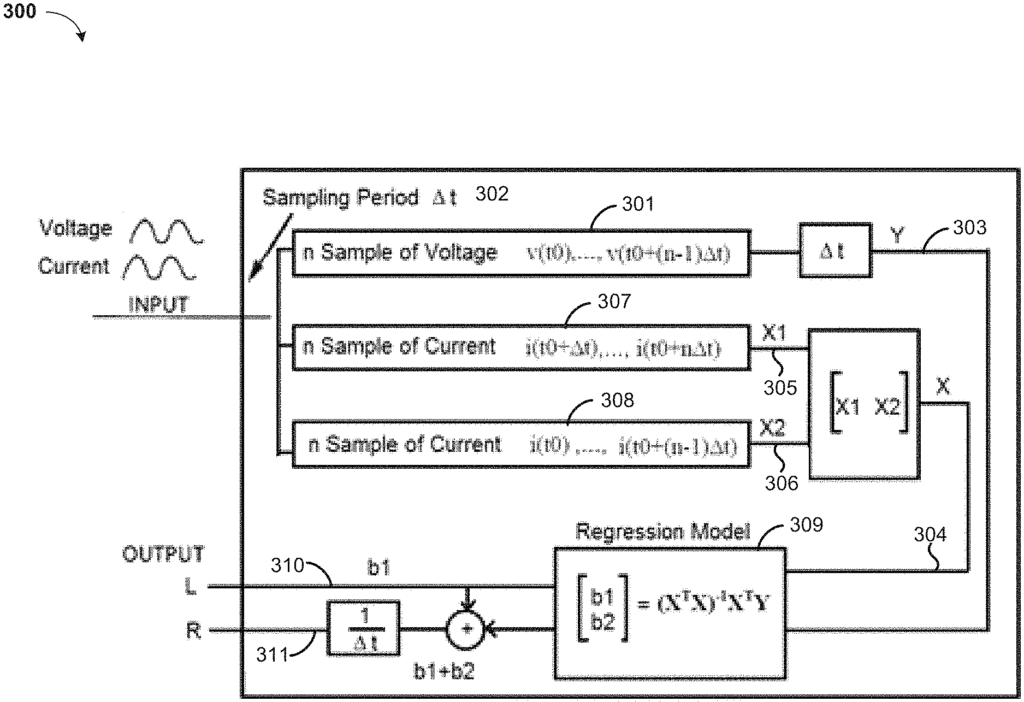

In the world of electronics and semiconductor manufacturing, circuit design is an essential yet complex task that demands precision, efficiency, and innovation. Determining the optimal values for circuit elements like resistors, capacitors, and inductors is a meticulous process that can significantly impact the performance and reliability of electronic devices. Our patented data generation method for regression models offers a transformative solution, automating and optimizing circuit element value determination to improve design outcomes and streamline production.

The Challenge of Circuit Element Value Determination

The design of electronic circuits requires selecting precise values for components that ensure optimal performance across various applications. Traditional methods of determining these values can be time-consuming, manual, and prone to errors, especially when dealing with highly complex circuits. For companies in the semiconductor and electronics industries, this challenge can lead to longer design cycles, higher costs, and less efficient manufacturing processes.

Given the increasing complexity of modern electronics, there is a growing need for tools that automate and improve the accuracy of these calculations. Without such innovations, designers may struggle to keep up with the demand for more efficient, reliable, and compact circuit designs.

Why Choose Efficient Circuit Design?

Our patented data generation method integrates advanced regression models to simplify the process of circuit element value determination. By analyzing data trends and optimizing calculations, this technology delivers faster, more accurate results. This leads to improved circuit performance, enhanced design efficiency, and lower production costs.

For electronics manufacturers, this technology reduces design time by automating the calculation of optimal component values, helping teams meet tight production deadlines. The method is highly adaptable and can be applied to a wide range of circuit types, from simple consumer electronics to complex semiconductors.

Key Benefits

- Faster Design Cycles: Automates the process of determining circuit element values, saving valuable time.

- Enhanced Precision: Uses regression models to improve accuracy in component selection.

- Cost-Effective: Reduces design errors and optimizes the manufacturing process.

- Versatile Applications: Applicable to a wide range of electronics, from simple circuits to advanced semiconductors.

Transform Circuit Design with Efficient Circuit Design Technology

Licensing this cutting-edge regression model technology offers electronics and semiconductor companies a powerful tool to streamline their design processes. With faster, more accurate calculations, this method helps reduce costs, shorten production times, and improve the overall performance of electronic devices.

- Abstract

- Claims

What is claimed is:

1. A method of transient fault detection in an electrical network, executable by a processor, comprising:

8. A computer system for transient fault detection in an electrical network, the computer system comprising:

15. A non-transitory computer readable medium having stored thereon a computer program for transient fault detection in an electrical network, the computer program configured to cause one or more computer processors to:

Share

Title

Data generation method for regression models for circuit element value determination

Inventor(s)

Charles J Kim

Assignee(s)

Howard University

Patent #

11782084

Patent Date

October 10, 2023